verilog 按位取反_搜索_中华文本库

109x154 - 5KB - JPEG

我有一端verilog截位程序不太明白,请高手帮忙

656x616 - 59KB - JPEG

基于verilog设计的双向32位移位寄存器.doc

993x1404 - 171KB - PNG

用verilog编写16位加法器乘法器自动售货机.do

794x1123 - 12KB - PNG

verilog奇偶校验位生成器 Verilog语言设计一个

1080x810 - 68KB - JPEG

verilog奇偶校验位生成器 Verilog语言设计一个

1080x810 - 76KB - JPEG

基于Verilog―A的14位200MHZ电流舵DAC建模

141x200 - 12KB - PNG

基于Verilog HDL的10位超前进位加法器计_中

1266x1987 - 516KB - PNG

基于Verilog计算精度可调的整数除法器的设计

521x634 - 52KB - JPEG

![verilog 有符号数运算在下面的代码中:reg [0:5]](http://img.zuoyesou.com/2016-05/26/1464263928.jpg)

verilog 有符号数运算在下面的代码中:reg [0:5]

600x338 - 17KB - JPEG

从电路到Verilog | 数字电路设计:有理论、有电

500x396 - 24KB - JPEG

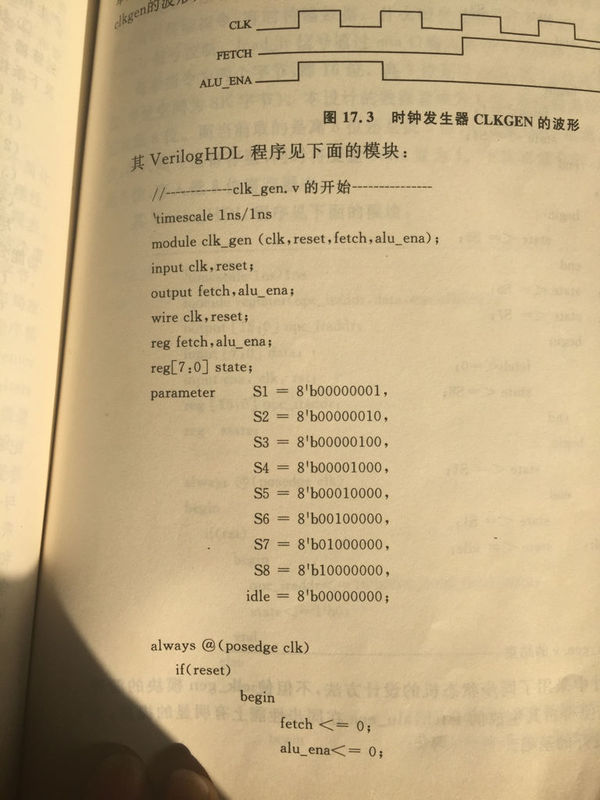

verilog hdl学习经典教程之一PPT

1080x810 - 131KB - JPEG

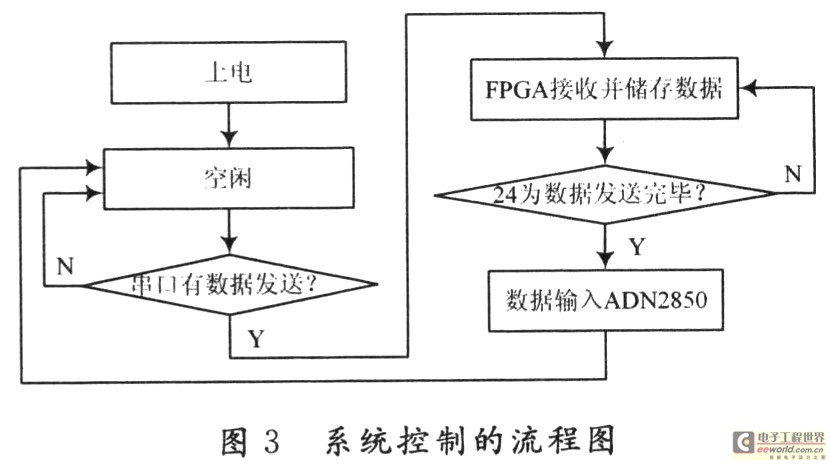

基于Verilog HDL数字电位器ADN2850的串口控

830x466 - 53KB - JPEG

哪位专业人士帮我把这个程序语句注释一下。这

600x800 - 62KB - JPEG

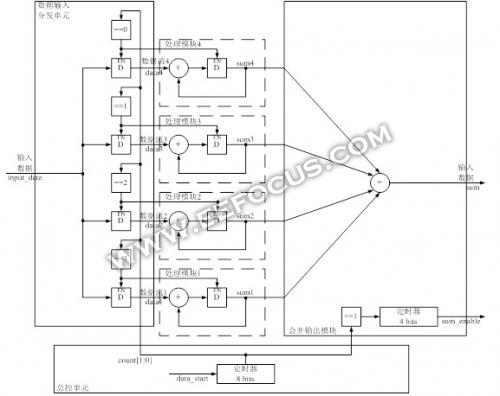

基于VerilogHDL的FIR数字滤波器设计与仿真

500x264 - 16KB - JPEG

后面是与门运算(按位与) 5'b10000&5'b10001 结果为1 5'b10000&b'b10001 结果为5'b10000

例如: wire[9:0]data_out;wire[6:03{data_in_a[6]}也要用{}括起来,要这样: assign data_out={{3{data_in

Verilog中&与&的区别.Verilog中&与&按位与 赋值运算 逻辑与 做条件判断用 while(a&b) { };判断a和b与完后

按位逻辑运算符,对操作数的每一个bit都进行相应的逻辑运算,操作数有多少bit,其运算结果就有多少bit。

casex({se0,se1,se2,se3})4'b1xxx:z按位取反~、按位与&、按位或|、按位异或^、按位同或^ 在不同长度的数据

Verilog-1995中的有符号数 在Verilog-1995中,只有integer数据类型被转移成有符号数,而reg和wire数据类型

两位加法器verilog HDL用门电路设计,解决方案1:参考代码如下,module add_1bit(a,b,ci,s,co)input a,b,ci;

所谓综合,就是把描述语言转化成能硬件实现的电路,学verilog的时候,没有人给我说要不要考虑能否综合的