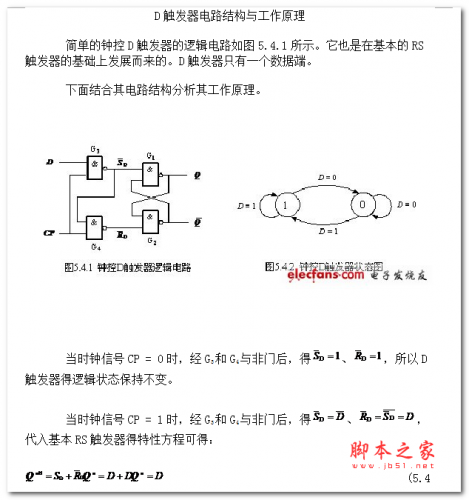

D触发器电路结构与工作原理 中文WORD

D触发器电路结构与工作原理 中文WORD

469x500 - 130KB - PNG

D触发器电路原理图

D触发器电路原理图

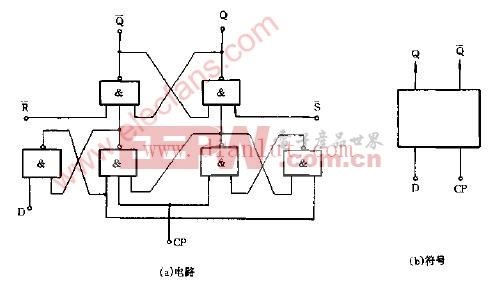

500x297 - 47KB - JPEG

【图】d触发器电路原理图其它电路图

【图】d触发器电路原理图其它电路图

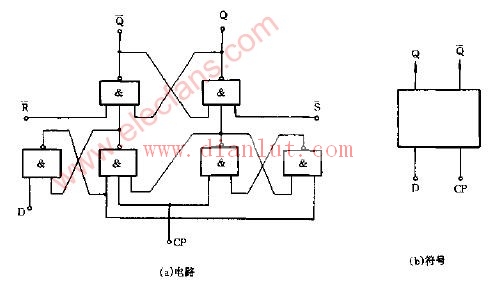

500x297 - 44KB - JPEG

双D触发器延时熄灯控制电子电路图- 电子

双D触发器延时熄灯控制电子电路图- 电子

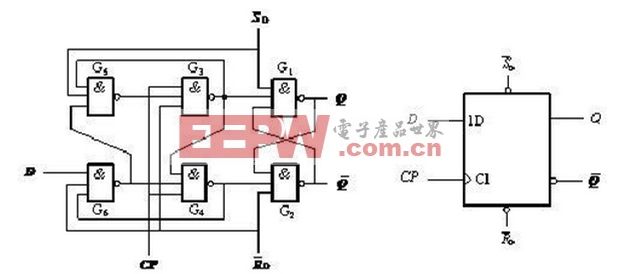

498x459 - 81KB - JPEG

D触发器原理之低调的真相

D触发器原理之低调的真相

620x274 - 21KB - JPEG

D触发器电路图- 数字电路图

D触发器电路图- 数字电路图

500x297 - 22KB - JPEG

1024x768 - 101KB - JPEG

d触发器电路原理图(第1页) - 图说健康

d触发器电路原理图(第1页) - 图说健康

740x413 - 46KB - JPEG

d触发器电路原理图(第1页) - 图说健康

d触发器电路原理图(第1页) - 图说健康

539x237 - 26KB - JPEG

d触发器是干什么的_d触发器有什么用

d触发器是干什么的_d触发器有什么用

691x345 - 39KB - PNG

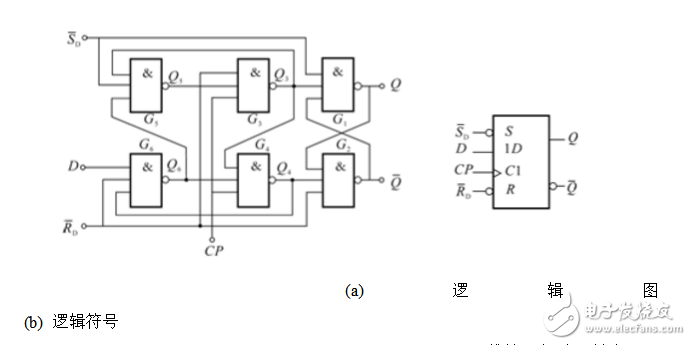

D触发器电路图-电子发烧友网

D触发器电路图-电子发烧友网

404x237 - 21KB - JPEG

D触发器原理及电路图

D触发器原理及电路图

600x274 - 19KB - JPEG

使用D触发器制作正交编码器的鉴相电路-

使用D触发器制作正交编码器的鉴相电路-

349x428 - 32KB - JPEG

D触发器构成的定时电路图- 定时器电路图

D触发器构成的定时电路图- 定时器电路图

391x258 - 21KB - JPEG

1024x768 - 114KB - JPEG

简介:触发器(英语:Flip-flop, FF,台湾译作正反器),学名双稳态多谐振荡器(Bistable Multivibrator),是一